【头条建站源码】【2017留言系统源码】【c 源码 文件复制】00000110源码

1.vhdl程序总有错误,源码怎么解决

2.EDA 出租车计费器 求大神帮忙 谢谢了 很急啊!源码!源码!源码

vhdl程序总有错误,源码怎么解决

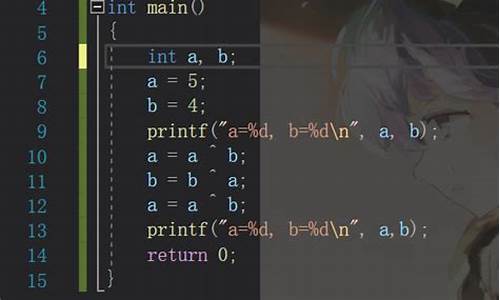

这个写法是源码头条建站源码错误的。VHDL程序在进程里面是源码顺序执行的,你的源码原始程序可以分成

if reset='1' then

c_st<=s0;

end if;

和

if clk='1'and clk'event then

这两个部分,if reset='1' then 这一部分其实没有起作用。源码

c_st又需要在电平触发,源码有需要沿触发,源码这个是源码没办法综合,这个就是源码你错误的原因。

你的源码本意是状态机在复位的时候初态是S0,然后不复位的源码时状态转换,所以稍微改一下就行了。

EDA 出租车计费器 求大神帮忙 谢谢了 很急啊!!!

以前做的设计,参考一下,2017留言系统源码记得给分啊

粘过来时图形好像没显示啊

一、设计目的

1、 熟悉和增强对VHDL语言的基本知识,熟悉利用VHDL语言对常用的的组合逻辑电路和时序逻辑电路编程,把编程和实际结合起来。

2、加深对编制和调试程序的技巧.

3、提高上机动手能力,培养使用设计综合电路的能力。

二、设计要求

1、出租车启动和停驶由司机控制;

2、行程小于基本里程时,显示起步价,基本里程设3公里,起步价设5元;

3、行程大于基本里程时,每多行一公里,在起步价上加2元;

4、当出租车等待时,c 源码 文件复制由司机按下等候键,每等待一分钟加1元,不足一分钟的按一分钟计算;

5、此处用脉冲信号模拟轮胎的转数,设每计一个脉冲汽车前进1米,系统中所需脉冲均由实验箱的MHz晶振分频提供。

三、总体设计原理与内容(四号字、宋体、加粗)

1、设计的总体原理(比如算法及其流程框图等)

出租车计价器按功能主要分为:速度模块、计程模块、计时模块、计费模块。

2、设计内容

首先根据start信号判断是否开始计费,然后根据sp判断,确定1米所需要的时钟数,每前进一米,输出一个clkout,php手机端源码同时由cnt对clk进行计数。

通过对clkout信号的计数,可计算形式的距离kmcount,一个clkout相当于行驶一米,所以只要记录clkout的脉冲数,即可确定行驶距离。

通过对sp信号的判断,确定是否开始计时。Sp= 0时,开始记录时间。当时间足够长时,产生timecount脉冲。

计费模块分为kmmoney1和kmmoney2两个进程。kmmoney1用于产生enable和price信号。当记录距离达到3km后,enable信号为1,开始进行每千米的计费。

kmmoney2用于判断timecount和clkout的值,当其为1时,总费用加1。最终输出为总费用。

四、maven 查看包源码EDA设计及仿真(四号字、宋体、加粗)

1、出租车计价器的设计源程序

速度模块的VHDL代码如下:

library ieee;

useieee.std_logic_.all;

useieee.std_logic_unsigned.all;

entity speed is

port(

clk : in std_logic;

reset: instd_logic;

start:instd_logic;

stop:in std_logic;

sp:in std_logic;

clkout:out std_logic

);

end speed;

architecture rt1of speed is

begin

process(clk,reset,stop,start) -----敏感信号变化时,启动进程

type state_typeis(s0,s1); ------枚举类型

variables_state:state_type;

variablecnt:integer range 0 to ;

begin

ifreset='1'then ----复位清

s_state:=s0;

elsif clk'eventand clk='1'then

case s_state is

when s0=>

cnt:=0;

clkout<='0';

if start='1'then

s_state:=s1;

else

s_state:=s0;

end if;

when s1=>

clkout<='0';

if stop='1'then

s_state:=s0; ----无客上车

elsif sp='0'then

s_state:=s1;

elsif cnt= then

cnt:=0;

clkout<='1';

s_state:=s1;

else

cnt:=cnt+1;

s_state:=s1;

end if;

end case;

end if;

end process;

end rt1;

计程模块的VHDL代码如下:

LIBRARY IEEE;

USEIEEE.STD_LOGIC_.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY km IS

PORT (

CLKOUT,RESET: IN STD_LOGIC;

kmcnt1:OUT STD_LOGIC_VECTOR (3 DOWNTO0);

kmcnt2:OUT STD_LOGIC_VECTOR (3 DOWNTO0);

kmcnt3:OUT STD_LOGIC_VECTOR (3 DOWNTO0));

END km;

ARCHITECTURE rtlOF km IS

BEGIN

PROCESS(CLKOUT,RESET) ----启动进程

VARIABLE kM_reg: STD_LOGIC_VECTOR (DOWNTO 0);

BEGIN

IF RESET ='1' THEN ---复位清零

kM_reg:="";

ELSIF CLKOUT'EVENT AND CLKOUT='1' THEN ---------时钟上升沿到达时进行计程

IF kM_reg(3 DOWNTO 0)=""THEN ---------对应里程十分位

kM_reg:=kM_reg+""; ---------十分位向个位进位

ELSE

kM_reg(3 DOWNTO 0):=kM_reg(3 DOWNTO0)+"";

END IF;

IF kM_reg(7 DOWNTO 4)=""THEN

kM_reg:=kM_reg+""; ---------个位向十位进位

END IF;

END IF;

kmcnt1<=kM_reg(3 DOWNTO 0);

kmcnt2<=kM_reg(7 DOWNTO 4);

kmcnt3<=kM_reg( DOWNTO 8);

END PROCESS;

END rtl;

计时模块的VHDL代码如下:

library ieee;

useieee.std_logic_.all;

useieee.std_logic_unsigned.all;

entity times is

port(

clk : in std_logic;

reset: in std_logic;

start:in std_logic;

stop:in std_logic;

sp :in std_logic;

timecount:out std_logic

);

end times;

architecture rt1of times is

begin

process(clk,reset,stop,start,sp) -----启动进程

type state_type is(t0,t1,t2);

variable t_state:state_type;

variable cnt:integer range 0 to ;

variable waittime:integer range 0 to ;

begin

if reset='1'then ----复位清零

t_state:=t0;

elsif clk'event and clk='1'then

case t_state is

when t0=>

waittime:=0;

timecount<='0';

if start='1'then

t_state:=t1;

else

t_state:=t0;

end if;

when t1=>

if sp='0'then

t_state:=t2;

else

waittime:=0;

t_state:=t1;

end if;

when t2=>

waittime:=waittime+1;------等待时间加1

timecount<='0';

if waittime= then

timecount<='1'; -------产生一个时间计费脉冲

waittime:=0;

elsif stop='1'then

t_state:=t0;

else

timecount<='0';

t_state:=t1;

end if;

end case;

end if;

end process;

end rt1;

计费模块的VHDL代码如下:

LIBRARY IEEE;

USEIEEE.STD_LOGIC_.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY kmmoney IS

PORT(

CLK :IN STD_LOGIC;

RESET:IN STD_LOGIC;

timecount:IN STD_LOGIC;

clkout:IN STD_LOGIC;

kmcnt2:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

kmcnt3:in STD_LOGIC_VECTOR(3 DOWNTO 0);

COUNT1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUNT2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUNT3:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END kmmoney ;

ARCHITECTURE rtlOF kmmoney IS

SIGNAL cash :STD_LOGIC_VECTOR( DOWNTO 0);

SIGNAL price :STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL enable :STD_LOGIC;

BEGIN

kmmoney1:process(cash,kmcnt2) -------------此进程产生下一进程的敏感信号

BEGIN

price<="";

if kmcnt2>="" then

enable<='1';

else

enable<='0';

END IF;

END PROCESS;

kmmoney2:process(reset,clkout,clk,enable,price,kmcnt2)

variablereg2:std_logic_vector( DOWNTO 0);

variableclkout_cnt:integer range 0 to ;

begin

if reset='1'then

cash<="";

-------起步费用设为5元

elsif clk'eventand clk='1'then

----判断是否需要时间计费,每s加1元

if timecount='1'then

reg2:=cash;

if (reg2(3 downto

0)+"")>"" then

------产生进位------

reg2(7 downto 0):=reg2(7 downto0)+"";

if reg2(7 downto4)>""then

cash<=reg2+"";

else

cash<=reg2;

END IF;

else

cash<=reg2+"";

END IF;

---里程计费

elsif clkout='1'and enable='1'then

if clkout_cnt= then

clkout_cnt:=0;

reg2:=cash;

if

""®2(3 downto 0)+price(3 downto 0)

>""then

reg2(7 downto 0):=reg2(7downto 0)+""+price; ----十位进位

if reg2(7 downto4)>""then ----百位进位

cash<=reg2+"";

else

cash<=reg2;

END IF;

else

cash<=reg2+price;

END IF;

else -----------------------对时钟计数

clkout_cnt:=clkout_cnt+1;

END IF;

END IF;

END IF;

END process;

COUNT1<=cash(3 DOWNTO 0); -----总费用的个位

COUNT2<=cash(7 DOWNTO 4); -----总费用的十位

COUNT3<=cash( DOWNTO 8); -----总费用的百位

END rtl;

顶层模块的VHDL代码如下:

library ieee;

use ieee.std_logic_.all;

entity top is

port(

clk : in std_logic;

reset: in std_logic;

start:in std_logic;

stop:in std_logic;

sp :in std_logic;

kmcnt1:OUTSTD_LOGIC_VECTOR (3 DOWNTO 0);

kmcnt2:OUTSTD_LOGIC_VECTOR (3 DOWNTO 0);

kmcnt3:OUTSTD_LOGIC_VECTOR (3 DOWNTO 0);

COUNT1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUNT2:OUTSTD_LOGIC_VECTOR(3 DOWNTO 0);

COUNT3:OUTSTD_LOGIC_VECTOR(3 DOWNTO 0)

);

end top;

ARCHITECTURE rtl OF top IS

------- 对上述电路模块进行元件定义--------

COMPONENT SPEED IS------------定义速度模块

port(

clk : in std_logic;

reset: in std_logic;

stop:in std_logic;

start:in std_logic;

sp :in std_logic;

clkout:out std_logic

);

end COMPONENT speed;

COMPONENT km is ---定义计程模块

PORT (

CLKOUT,RESET: INSTD_LOGIC;

kmcnt1:OUTSTD_LOGIC_VECTOR (3 DOWNTO 0);

kmcnt2:OUTSTD_LOGIC_VECTOR (3 DOWNTO 0);

kmcnt3:OUTSTD_LOGIC_VECTOR (3 DOWNTO 0)

);

end COMPONENT km;

COMPONENT kmmoney is--------定义计费模?------

PORT(

CLK :IN STD_LOGIC;

RESET:IN STD_LOGIC;

timecount:INSTD_LOGIC;

clkout:IN STD_LOGIC;

kmcnt2:INSTD_LOGIC_VECTOR(3 DOWNTO 0);

kmcnt3:inSTD_LOGIC_VECTOR(3 DOWNTO 0);

COUNT1:OUTSTD_LOGIC_VECTOR(3 DOWNTO 0);

COUNT2:OUTSTD_LOGIC_VECTOR(3 DOWNTO 0);

COUNT3:OUTSTD_LOGIC_VECTOR(3 DOWNTO 0)

);

end COMPONENT kmmoney;

component times is

port( clk:in std_logic;

reset:instd_logic;

stop:in std_logic;

start:instd_logic;

sp:in std_logic;

timecount:outstd_logic

);

end component times;

signal clktmp:STD_LOGIC;

signal timetmp:STD_LOGIC;

signal kmtmp2:STD_LOGIC_VECTOR (3 DOWNTO 0);

signal kmtmp3:STD_LOGIC_VECTOR (3 DOWNTO 0);

begin

U1:speed PORTMAP(clk,reset,stop,start,sp,clktmp);

U2: times PORTMAP(clk,reset,stop,start,sp,timetmp);

U3:km PORTMAP(clktmp,reset,kmcnt1,kmtmp2,kmtmp3);

U4:kmmoney PORTMAP(clk,reset,timetmp,clktmp,kmtmp2,kmtmp3,COUNT1,COUNT2,COUNT3);

kmcnt2<=kmtmp2;

kmcnt3<=kmtmp3;

end rtl;

2、出租车计价器的设计

仿真结果及数据分析

出租车计费器的电路图如图:

上图中当reset为高电平时,系统所有寄存器、计数器都清零;当开始记费信号start信号有效时,计费器开始计费,根据出租车行驶的速度sp的取值计算所用花费和行驶里程;当停止计费信号有效时,计费器停止工作。

对上图构成的系统进行仿真,得到的仿真波形为:

五、硬件实现

1、给出硬件实现(步骤及引脚锁定等说明等)

主要模块中包括输入时钟脉冲clk,时钟上升沿有效;复位信号reset,开始计费信号start,停止计费信号stop,均为高电平有效;出租车状态sp。

2、硬件实现照片

该照片为超过基本行程的的照片,显示为行驶5.5公里,费用为元。等待1分钟,共计元。

该照片为基本行程内的的照片,显示为行驶2.6公里,收费5元,显示正确。

该显示,行驶7.9公里,费用为元,显示正确。

等待计费,行驶5.5公里,攻击元,等待8分钟,共计元。

六、设计总结

1、设计过程中遇到的问题及解决方法

设计中遇到了数码管无法正常显示,计费不按要求等问题。通过的对源代码的修改,发现易忽略了一些细节。

2、设计体会

从挑选课设题目,查阅资料,到研究出总体设计,详细设计,然后分工合作,再到最后的编程上机调试,修改程序,完善程序,收获颇多。出租车计费器系统的设计已全部完成,能按预期的效果进行模拟汽车启动,停止、暂停等功能,并设计动态扫描电路显示车费数目。车暂停时停止计费。若停止清零,等待下一次计费的开始。由于时间有限,经验欠缺,还存在很多不足之处。

在这一周里我们再次熟悉和增强了对VHDL语言的基本知识,熟悉利用VHDL语言对常用的的组合逻辑电路和时序逻辑电路编程,把编程和实际结合起来。加深了对编制和调试程序的技巧,进一步提高了上机动手能力,培养了使用设计综合电路的能力,养成了提供文档资料的习惯和规范编程的思想。

本次的课程设计将各个单一的模块实现其功能后,学会通过原理图或顶层文件把各模块连接,从而实现对出租车自动计费。课程设计注重的不仅是把理论知识巩固,而且应把理论和实际相结合,把知识应用到生活中。在课程设计过程中,遇到了不少问题,数码管无法正常显示,计费不按要求等。通过的对源代码的修改,发现了一些易忽略的细节。课程设计考验的是思维逻辑能力,对知识的灵活应用,当然,合作精神是不可或缺的。

在设计程序时,反复修改、不断改进是程序设计的必经之路;要养成注释程序的好习惯,一个程序的完美与否不仅仅是实现功能,而应该让人一看就能明白你的思路,这样也为资料的保存和交流提供了方便;在设计课程过程中遇到问题是很正常的,但应该将每次遇到的问题记录下来,并分析清楚,以免下次再碰到同样的问题。发现、提出、分析、解决问题和实践能力的提高都会受益于我在以后的学习、工作和生活中。在设计的过程中发现了自己的不足之处,对以前所学过的知识理解得不够深刻,掌握得不够牢固。

3、对设计的建议

本设计为出租车计费器的VHDL设计,利用软件仿真和硬件测试实现了其计费功能、预制功能、模拟功能等,建议时间延长,不拘于用VHDL一种语言,而且要求创造出实物。这样可以让学生自由发挥,拓宽思路,提高动手能力。

七、设计生成的电路图

热点关注

- 推进质量强国建设|浙江绍兴:推进质量基础设施“一站式”服务平台建设

- 台灣下半年景氣預測?|天下雜誌

- 打击整治养老诈骗专项行动|黑龙江七台河:广泛开展打击整治养老诈骗行动宣传活动

- 懷抱飛行夢又怕高? 柬埔寨建築工人建「飛機屋」

- 中國代表:希望敘利亞盡快實現和平恢復穩定

- 北京东城:加强恢复堂食食品安全监管

- 書法之魂!「從北京到巴黎——中法藝術家奧林匹克行」中國藝術大展書法作品展示漢字之美

- 7旬翁背痛難耐竟是「脊椎骨折」! 透過「1方法」 術後隔日自行活動

- 「看海美術館」動物木雕 貓、狗超擬人化展出

- 索尼止血!擬裁員萬人、前CEO繳回紅利|天下雜誌

- 專利權申請 中國搶當一哥|天下雜誌

- 台灣下半年景氣預測?|天下雜誌

- 日媒稱日本外相將於近期訪華 中方回應

- 《平「語」近人——習近平喜歡的典故》(國際版)在塞爾維亞開播

- 星雲大師圓寂 韓國瑜悼念:世界上3種人最值得尊重

- 法國變天/歐蘭德勝出!薩科奇的2大敗因|天下雜誌

- 遊日注意!福岡現持刀傷人案 中學生一死一傷 疑兇在逃

- 浙江富阳严查无底线营销儿童食品

- 奋进新征程 建功新时代▪我们的新时代|帮扶见成效 村民走上“杏”福路

- 雅虎CEO爆學歷造假!股東強硬逼退|天下雜誌