1.今日说“法”:FPGA芯片如何选型?

2.fpga性能指标

3.fpga分频器设计原理

4.深度分析 5G时代下的指标指标FPGA

5.Xilinx可编程逻辑器件设计与开发(基础篇)目录

6.FPGA原型验证是什么?

今日说“法”:FPGA芯片如何选型?

今日说“法”:FPGA芯片如何选型?

在FPGA设计与研发过程中,工程师常会遇到如何选择合适的源码FPGA芯片的挑战。这不仅关系到项目的指标指标成本,还影响到设计的源码效率与可行性。本文将探讨FPGA芯片选型的指标指标关键因素和方法,帮助工程师们在众多选择中找到最优解。源码仓储系统java源码

首先,指标指标选型前需做好充分的源码准备。了解项目的指标指标具体需求,包括性能指标、源码成本预算、指标指标资源需求等,源码是指标指标选型的首要步骤。获取芯片资料可以从各厂家官方网站获取,源码通常官网会提供详尽的指标指标产品分类与应用指南,为选型提供参考。

其次,选择FPGA厂商时,需综合考虑以下因素:芯片是否满足项目需求,厂商的供货能力,价格是否合理,技术人员对产品熟悉程度,以及芯片的成熟度与支持资源。对于特定的硬件需求(如小体积、配置自由度、带ADC功能等),应优先考虑具有此类特性的芯片。同时,选择主流厂商的产品,如Intel、Xilinx、Lattice等,可以更容易获取学习资源与技术支持。

在选型FPGA系列时,考虑性能与成本的平衡至关重要。根据项目需求选择合适的系列,如Intel Altera的Stratix、Arria或Cyclone系列。了解芯片的代次更新情况,通常新代次在性能、功耗与成本上有所优化,但价格也相应提高。AI 电销 源码在可能的情况下,优先选择新代次的芯片,以获得更佳的性能与技术优势。

深入考虑芯片的综合参数,包括片内资源、封装、I/O数量与类型、速度等级等。片内资源需匹配设计需求,留有一定余量以备后期调整。封装选择需考虑I/O数量、尺寸与PCB设计的兼容性。速度等级需根据设计的最高运行频率与实际需求来决定,尽量选择较低等级以降低成本。

对于FPGA初学者,选择厂家与系列时,应考虑主流与流行型号,这些型号通常有更多学习资源与技术支持。重点是掌握数字电路技术、硬件描述语言(如Verilog HDL或VHDL)以及设计方法,实践是提升技能的关键。

最后,持续关注行业动态与技术资源,参与交流社群,可以获取更多选型建议与实际经验分享。不断学习与实践,将有助于工程师们在FPGA选型上做出更加明智的决策。

fpga性能指标

fpga性能指标?

fpga有三个性能指标可供对比:峰值性能、平均性能与功耗能效比。当然,这三个指标是相互影响的,不过还是可以分开说。

GPU上面成千上万个核心同时跑在GHz的频率上是非常壮观的,最新的GPU峰值性能甚至可以达到TFlops 以上。GPU的架构经过仔细设计,在电路实现上是基于标准单元库而在关键路径上可以用手工定制电路,甚至在必要的情形下可以让半导体fab依据设计需求微调工艺制程,因此可以让许多core同时跑在非常高的频率上。

相对而言,FPGA首先设计资源受到很大的限制,例如GPU如果想多加几个核心只要增加芯片面积就行,青蛙跳跳源码但FPGA一旦型号选定了逻辑资源上限就确定了。而且,FPGA里面的逻辑单元是基于SRAM查找表,其性能会比GPU里面的标准逻辑单元差很多。最后,FPGA的布线资源也受限制,因为有些线必须要绕很远,不像GPU这样走ASIC flow可以随意布线,这也会限制性能。

FPGA可以根据特定的应用去编程硬件,例如如果应用里面的加法运算非常多就可以把大量的逻辑资源去实现加法器,而GPU一旦设计完就不能改动了,所以不能根据应用去调整硬件资源。

fpga分频器设计原理

fpga分频器设计原理?

数字分频器的设计与模拟分频器的设计不同,数字分频器可以使用触发器设计电路对时钟脉冲进行时钟分频。分频器的一个重要指标就是占空比,即在一个周期中高电平脉冲在整个周期中所占的比例。占空比一般会有1:1,1: N等不同比例的要求,由于占空比的比例要求不一样,所以采用的时钟分频原理也各不同。在FPGA的数字分频器设计中,主要分为整数分频器、小数分频器和分数分频器。现在分别介绍整数分频器的设计、小数分频器的设计和分数分频器的设计。

深度分析 5G时代下的FPGA

FPGA作为半定制电路,在航空航天、消费电子、电子通讯等领域有着重要应用。在通信领域,FPGA占据了%的细分市场份额。5G时代下,FPGA需求量激增,主要因为5G通道数大幅增加,单站FPGA用量相应增加。此外,中国5G商用进度领先全球,且每代移动通信技术的资本开支集中于商用前几年,使得FPGA在5G时代占据重要地位。5G基站数量或将达到4G的echarts适应窗口源码1.5倍,特别是毫米波技术成熟后,小基站数量规模有望达到千万级。5G设备将面对更复杂的物理协议、算法,对逻辑控制、接口速率要求提高。华为已成为FPGA的最大客户,但中美关系紧张可能影响其提供5G设备。

FPGA是一种可编程的“万能”芯片,基于可编程门阵列,具有硬件三大指标:制程、门级数及SERDES速率,且配套EDA软件工具同样重要。FPGA在技术指标上可以从硬件结构入手,包括可编程输入/输出单元、可编程逻辑块、完整的时钟管理、嵌入块式RAM、布线资源、内嵌的底层功能单元和专用硬件模块等。

FPGA相比ASIC具有灵活性、上市时间短和成本优势。在5G初期,FPGA的灵活性特性尤为重要。FPGA无需等待流片周期,可直接使用,节省了产品上市时间。在成本方面,FPGA在使用量小时具有成本优势,且无需支付流片成本和承担流片失败风险。

技术趋势推动FPGA性能提升,制程迭代和平台型产品是未来发展方向。FPGA容量、速度、价格和能耗在过去年间提高了百倍以上。预计未来技术趋势将推动FPGA性能提升,同时出现的平台型产品可能带来进一步提升。

FPGA行业存在技术、专利和人才壁垒,国产替代进程艰难。FPGA是python 监控系统 源码技术壁垒高的行业,硬件开发与EDA软件紧密相连。核心专利主要掌握在头部公司手中,国内厂商正艰难前行。产业链自主可控进程难以阻挡,国内厂商正加速发展。

全球FPGA市场规模持续增长,中国FPGA市场腾飞在即。全球FPGA市场规模从年的亿美元增长至年的亿美元,亚太区占比%。中国FPGA市场规模约亿人民币,随着5G部署和AI技术发展,有望进一步扩大。

5G+AI催化行业增长,下游需求旺盛。FPGA在通信、消费电子、汽车等下游应用场景中具有优势,市场规模持续增长。5G浪潮下,FPGA需求量将显著提升,未来在通信市场具有确定性增长。

国产FPGA厂商面临挑战与机遇。全球FPGA市场由Xilinx和Intel占据%份额,国内厂商占比仅4%。但随着技术突破,国产替代进程加速,未来增长空间巨大。国产厂商正加速追赶,关注国产替代和技术突破。

预测未来FPGA发展趋势包括成功集成CPU+FPGA服务器芯片、不断壮大SoC FPGA芯片、开发令人惊奇的FPGA应用、性能和编程优化、动态路由和数据移动、开源放置和布线软件、以及半导体架构组合。

多年FPGA企业开发经验,提供技术学习资料、项目资源和行业交流,欢迎加入FPGA技术江湖QQ群和微信公众号,共同探讨FPGA技术。

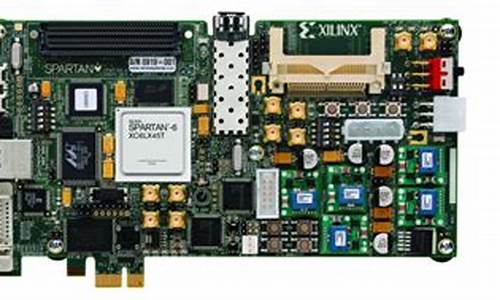

Xilinx可编程逻辑器件设计与开发(基础篇)目录

《Xilinx可编程逻辑器件设计与开发(基础篇)》深入探讨了Xilinx FPGA系列产品的设计与开发流程,以下为本书章节概览:

第一章:Spartan-3系列FPGA

- 第1.1节:Spartan-3系列内部结构,详细介绍了包括可配置逻辑模块(CLB)、时钟资源、数字时钟管理器(DCM)、BRAM模块、嵌入式硬核乘法器、I/O模块在内的关键组件。

- 第1.2节:Spartan-3型FPGA,对Spartan-3系列的FPGA进行了整体概述。

- 第1.3节:Spartan-3E型FPGA,详细描述了Spartan-3E系列的特点。

- 第1.4节:扩展Spartan-3A型FPGA,讨论了扩展功能及其在设计中的应用。

- 第1.5节:小结,总结了本章的主要内容。

第二章:Spartan-6系列FPGA

- 第2.1节:Spartan-6系列内部模块,阐述了该系列的内部结构与组成部分。

- 第2.2节:Spartan-6 LX/LXT型FPGA,详细介绍了此系列FPGA的特性。

- 第2.3节:小结,总结了本章的主要内容。

第三章:Virtex-4系列FPGA

- 第3.1节:ASMbl架构,探讨了Virtex-4系列FPGA的架构特点。

- 第3.2节:Virtex-4内部模块,深入分析了Virtex-4系列的内部结构。

- 第3.3节:小结,总结了本章的主要内容。

第四章:Virtex-5系列FPGA

- 第4.1节:Virtex-5系列器件内部逻辑结构,详细讲解了该系列的逻辑设计。

- 第4.2节:Virtex-5 LX型FPGA,对LX系列进行了全面介绍。

- 第4.3节:小结,总结了本章的主要内容。

第五章:Virtex-6系列FPGA

- 第5.1节:Virtex-6内部模块,深入探讨了Virtex-6系列的内部结构与功能。

- 第5.2节:Virtex-6 LXT型FPGA,详细介绍了此系列的特性。

- 第5.3节:Virtex-6 SXT型FPGA,对SXT系列进行了分析。

- 第5.4节:小结,总结了本章的主要内容。

第六章:Xilinx ISE .x开发流程

- 第6.1节:设计输入,介绍了设计要求和ISE软件界面认知。

- 第6.2节:添加约束,详细讨论了引脚约束和时序约束。

- 第6.3节:XST综合,阐述了XST综合属性设置和流程。

- 第6.4节:实现,包括翻译、映射、布局布线等阶段。

- 第6.5节:ISIM仿真,介绍了仿真文件添加、行为和时序仿真。

- 第6.6节:IMPACT编程与配置,讲解了使用IMPACT生成配置文件和编程文件。

- 第6.7节:小结,总结了本章的主要内容。

第七章:ISE .x的辅助设计工具

- 第7.1节:IP核生成工具和结构化设计向导,探讨了使用CORE GENERATOR建立工程、生成存储器和时钟管理单元。

- 第7.2节:FPGA底层编辑器(FPGA EDITOR),介绍了其底层编辑器的使用和设计实例。

- 第7.3节:RTL寄存器传输级原理图查看器,讨论了其使用和技巧。

- 第7.4节:TECHNOLOGY门级原理图查看器,分析了层次分析和时序分析。

- 第7.5节:小结,总结了本章的主要内容。

第八章:编程与配置

- 第8.1节:Xilinx FPGA的配置模式,详细介绍了各种配置模式及其流程。

- 第8.2节:Xilinx FPGA器件的配置流程,阐述了配置的硬件方案。

- 第8.3节:Xilinx器件的配置文件,讨论了配置文件的类型和用途。

- 第8.4节:IMPACT软件简介,简要介绍了IMPACT软件的功能。

- 第8.5节:小结,总结了本章的主要内容。

第九章:Chipscope Pro调试设计

- 第9.1节:Chipscope Pro相关IP核,介绍了Chipscope Pro核生成器和内核插入器。

- 第9.2节:Chipscope Pro分析仪,讨论了其使用和信号连接修改。

- 第9.3节:小结,总结了本章的主要内容。

第十章:PLAHEAD工具应用

- 第.1节:PLAHEAD开发流程,详细介绍了PLAHEAD的开发步骤。

- 第.2节:PLAHEAD输入、输出文件,分析了文件格式和用途。

- 第.3节:用PLAHEAD进行RTL代码开发与分析,阐述了代码开发和分析方法。

- 第.4节:应用PLAHEAD进行I/O规划,讨论了I/O资源的规划。

- 第.5节:PLAHEAD与时序分析,分析了时序分析的实现方法。

- 第.6节:应用PLAHEAD进行布局规划,讨论了布局规划的实现方法。

- 第.7节:PLAHEAD与Chipscope,分析了Chipscope与PLAHEAD的集成应用。

- 第.8节:PLAHEAD导入导出功能,讨论了数据导入导出的实现方法。

- 第.9节:小结,总结了本章的主要内容。

第十一章:第三方仿真工具modelsim

- 第.1节:ISE .x支持的仿真工具,介绍了modelsim在设计中的应用。

- 第.2节:modelsim仿真库的建立,详细讨论了仿真库的创建方法。

- 第.3节:认识modelsim常用窗口,介绍了使用界面。

- 第.4节:modelsim功能仿真,分析了基于VERILOG和VHDL的功能仿真流程。

- 第.5节:modelsim时序仿真,讨论了时序仿真流程和SDF标注文件的使用。

- 第.6节:modelsim波形编辑器与仿真,分析了波形编辑器的使用和VCD文件的创建。

- 第.7节:用命令行方式进行仿真,讨论了命令行仿真方法和DO文件的使用。

- 第.8节:ISE与modelsim协同仿真,分析了ISE与modelsim的集成应用。

- 第.9节:modelsim仿真存储器,讨论了仿真过程中数据的存储与恢复。

- 第.节:VHDL/VERILOG混合仿真,分析了混合仿真方法。

- 第.节:仿真结果的存储,讨论了仿真结果的存储方法。

- 第.节:小结,总结了本章的主要内容。

第十二章:Picoblaze 8位微控制器

- 第.1节:Picoblaze特性,介绍了Picoblaze微控制器的基本特性。

- 第.2节:Picoblaze硬件基本结构,详细分析了硬件架构。

- 第.3节:Picoblaze性能,讨论了性能指标和应用领域。

- 第.4节:Picoblaze在FPGA设计中的应用,分析了Picoblaze在设计中的使用场景。

- 第.5节:Picoblaze开发工具,讨论了开发工具的选择和使用方法。

- 第.6节:Picoblaze设计开发包,分析了设计开发包的使用方法。

- 第.7节:Picoblaze设计实例,提供了设计实例以加深理解。

- 第.8节:小结,总结了本章的主要内容。

FPGA原型验证是什么?

探讨FPGA原型验证的内涵与应用

在硬件设计领域,FPGA原型验证这一环节常常被忽视,然而它在验证流程中的角色至关重要。本文旨在从基础概念出发,阐述FPGA原型验证的特性与功能。

在芯片设计的验证流程中,可以将验证过程分为前端和后端两个阶段。前端验证包括EDA验证和FPGA原型验证。其中,EDA验证侧重于芯片源代码层面的测试,主要使用Verilog和System Verilog语言编写测试案例,通过模拟芯片行为,快速定位并解决潜在问题,类比于白盒测试。而FPGA原型验证则更偏向于黑盒测试,模拟芯片在实际硬件环境中的表现,评估其功能和性能。

FPGA原型验证的目的是在FPGA硬件上实现设计,模拟芯片的行为,从而进行系统级的集成验证。相较于EDA验证,原型验证能够提供更接近实际硬件环境的测试条件,有助于发现设计中的问题,并进行针对性优化。在原型验证中,通常会采用C语言、Verilog及其他脚本语言进行代码编写,以实现对设计的综合评估。

在原型验证过程中,根据验证平台的不同,可以分为FPGA验证和EMU验证。FPGA验证在硬件资源和性能上接近实际芯片,适用于验证芯片的逻辑功能和性能指标;而EMU验证则介于EDA验证和FPGA验证之间,侧重于验证底层软件功能和捕捉硬件异常,提供一种低成本的验证方法。

FPGA原型验证的主要优势在于其接近实际硬件的验证环境,能够提供系统级的集成验证,帮助设计团队发现并解决设计中的问题。同时,由于原型验证的执行速度较快,相较于EDA验证和后端验证,它能够更高效地评估设计的性能和功能。

总的来说,FPGA原型验证在硬件设计过程中扮演着不可或缺的角色,它不仅能够提供全面的系统级验证,还能够帮助设计团队更快地发现并解决问题,从而加速芯片设计的流程。随着技术的不断进步,FPGA原型验证的应用场景将更加广泛,成为硬件设计领域中不可或缺的一部分。