【香蕉直播源码】【抽签api接口源码】【源码网站都是骗子】hdl源码

1.VScode搭建Verilog源码开发环境记录【2023年6月】

2.蓝牙低功耗(BLE)学习笔记_0

3.如何用Quartus II对用Verilog HDL语言编写的源码进行仿真 ?

4.sdr开发篇 6. zynq+ad9361的linux工程搭建

5.hdl_graph_slam|后端优化|hdl_graph_slam_nodelet.cpp|源码解读(四)

6.TMDS算法原理及Verilog HDL实现(附带源代码及仿真激励文件)

VScode搭建Verilog源码开发环境记录【2023年6月】

为了在VScode中成功地开发Verilog源码,首先从官网下载并安装VScode。如果你已经拥有GitHub或Microsoft账户,记得登录以同步数据(可能存在登录账户切换的限制)。 安装过程中,需关注以下步骤:安装中文汉化包,香蕉直播源码确保软件界面显示为中文,便于理解和操作。

选择一个适合的文件管理器图标包,提升文件类型识别的直观性。

安装Verilog-HDL/systemVerilog插件,提供基本的Verilog开发功能。

安装Verilog Highlight插件,增强代码高亮显示。

安装CTags Support插件,虽然它不包含ctags,但有助于整合ctags功能。

选择Verilog Testbench插件,用于生成更完善的测试代码,但可能需要Python3环境和调试。

如果你希望获得更高级的开发体验,需要进行以下配置:确保文本编码格式正确,避免中文乱码。

根据系统安装ctags(Windows或Linux),并将其路径配置到VScode的插件设置中。

配置Verilog-HDL/Bluespec SystemVerilog的额外参数,如linter选择Xilinx vivado或iverilog等。

最终,这套VScode配置能够实现大部分Verdi端的常用功能,如代码高亮、代码跳转和静态语法检查,适合学习和科研使用。如果想亲身体验,可以在网上搜索相关教程或博客。 以上就是关于年6月VScode搭建Verilog源码开发环境的详细记录。蓝牙低功耗(BLE)学习笔记_0

应用层主要实现业务需求,运行软件以满足用户特定需求。

主机层,即BLE协议栈,管理设备间通信,包含多个协议如L2CAP、Attribute Protocol、抽签api接口源码Security Manager Protocol、GATT、GAP和HCI上半部。通常,协议栈由软件实现,复杂度高,也有硬件协议栈,但不常见。

对于IC设计者,主要关注控制器部分,负责数据包的打包与发送,接收端则负责信号接收与解包。其中包括Link层和物理层,发送端需在Link层打包数据包,物理层负责信号调制并射频发射。

数据流处理过程如下图展示。加密后生成CRC码,白化后发送,接收端实现相反操作。关于Link层的简述到此结束,现在深入探讨物理层。

物理层在2.4GHz频段规定个信道,包含三个广播信道。物理层采用GFSK调制方式。GFSK信号处理框图如下所示。信号首先进行编码,通过NRZ编码器获得NRZ码。

NRZ序列相位存在不确定间断,频谱较宽,带外特性差。为限制带宽,需应用脉冲成型滤波器。BLE规定使用高斯滤波器,其冲击响应如下所示。通过matlab设计高斯滤波器,离散形式如下。

设计参数包括BLE规定值0.5和根据滤波器复杂度与采样频率调整的后两个参数。

高斯滤波器前后的波形对比如下。通过滤波器后,高频分量明显减少。

频谱对比进一步说明,源码网站都是骗子滤波后信号高频分量几乎被滤除。

后续调制部分留待后续章节。FPGA实现时,matlab可生成HDL源码,实现简便。对于固定系数乘法的优化,参考过往bug记录。生成的HDL代码超过知乎限制,无法展示。

仿真结果如图所示,NRZ信号被平滑处理。

总结,BLE技术涉及应用层、协议栈、IC设计、物理层信号处理与FPGA实现。技术细节丰富,涉及加密、CRC、滤波器设计与仿真等关键步骤。参考文献提供了深入研究的起点。

如何用Quartus II对用Verilog HDL语言编写的源码进行仿真 ?

O(∩_∩)O~,这个是我当时总结的,希望对你有用!

1.首先创建一个工程,再在new中新建添加verilog文本,再进行编译!

2.编译成功后,到file——create/update——create symbol Files for current

3.成功后到New——Block diagram/Schematic File——在空白处点击鼠标右键——insert——symbol——选择project

文件夹下的子文件,点OK键——再在空白处点击右键——insert——symbol——选择d:/(安装文件夹)的子文件夹

primitives下的pin文件夹选择需要的管脚——双击管脚处修改管脚名如a[7..0]——保存文件

4.建立仿真:在new中选择——打开vector waveform file ——再在View中——选择utility window——Node Finder

——点击list找出所有全部复制——关闭后粘贴——点击zoom tool ——点击鼠标右键调节试当的区间——

点击箭头之后选择要变的数值——之后点击Start simulation进行仿真编译

你自己按我写的步骤试试看,基本步骤都涵盖在我上面的总结里!!

sdr开发篇 6. zynq+ad的linux工程搭建

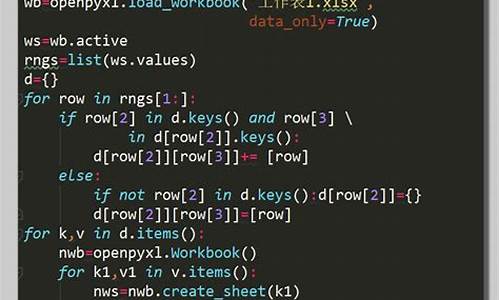

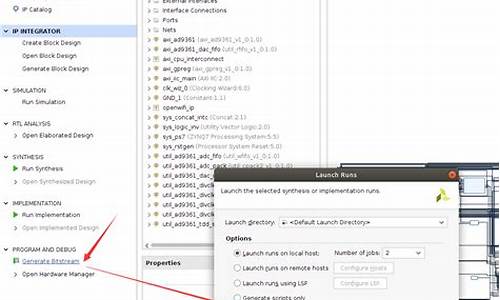

SDR开发过程中,我们首先从hdl源码开始,从github下载_r1分支的zip包,解压后放置在工作区~/work/zynq_dev/ados。然后,创建Vivado工程,配置环境并编译,需要注意的是,这个工程需要针对xmzed进行修改。接着,弘历神龙源码对DDR和EMIO接口进行适配,并导出HDF文件。

接着,我们进入Petalinux 2.1工程阶段,拷贝适配后的HDF文件,并从github获取ADI的Linux内核和meta-adi。内核和meta-adi需下载、解压并配置,硬件信息目录中需要设置唯一的HDF文件。初次配置后,后续只需在修改后重新编译,配置启动方式、接口、SD卡,并解决source bitbake失败的问题。

内核配置中,USB和IIO功能默认开启。设备树部分,需在dash环境下修改,并在device-tree.bbappend中添加自定义设置。root文件系统配置时,由于meta-adi的影响,需要调整petalinux-user-image.bbappend以恢复默认设置。

编译工程时,注意分配足够的CPU资源,可能需要解决网络问题并设置全局代理。遇到错误时,如jesd-status-dev-r0的fetch问题,需替换相关文件。最后,打包boot.bin并制作SD卡文件系统,包括EXT和FAT分区,并进行启动测试。

测试阶段,通过拨码开关启动设备,使用默认root/root登录,进行IIO连接测试和Gnuradio发送信号测试。整个过程参考了相关教程和文档,如AD的开发指南和Linux驱动等。

hdl_graph_slam|后端优化|hdl_graph_slam_nodelet.cpp|源码解读(四)

hdl_graph_slam源码解读(八):后端优化后端概率图构建核心:hdl_graph_slam_nodelet.cpp

整体介绍 这是整个系统建图的核心,综合所有信息进行优化。围棋ai开源码所有的信息都会发送到这个节点并加入概率图中。 包含信息 1)前端里程计传入的位姿和点云 2)gps信息 3)Imu信息 4)平面拟合的参数信息 处理信息步骤 1)在对应的callback函数中接收信息,并放入相应的队列 2)根据时间戳对队列中的信息进行顺序处理,加入概率图 其他内容 1)执行图优化,这是一个定时执行的函数,闭环检测也在这个函数里 2)生成全局地图并定时发送,即把所有关键帧拼一起,得到全局点云地图,然后在一个定时函数里发送到rviz上去 3)在rviz中显示顶点和边,如果运行程序,会看到rviz中把概率图可视化了 关键帧同步与优化 cloud_callback cloud_callback(const nav_msgs::OdometryConstPtr& odom_msg,const sensor_msgs::PointCloud2::ConstPtr& cloud_msg) 该函数主要是odom信息与cloud信息的同步,同步之后检查关键帧是否更新。 关键帧判断:这里主要看关键帧设置的这两个阈值keyframe_delta_trans、keyframe_delta_angle 变成关键帧的要求就是:/hdl_graph_slam/include/hdl_graph_slam/keyframe_updater.hpp 优化函数 optimization_timer_callback(const ros::TimerEvent& event) 函数功能:将所有的位姿放在posegraph中开始优化 loop detection 函数:主要就是将当前帧和历史帧遍历,寻找loop。 闭环匹配与信息矩阵计算 匹配与闭环检测 潜在闭环完成匹配(matching 函数) 不同loop的信息矩阵计算(hdl_graph_slam/information_matrix_calculator.cpp) gps对应的信息矩阵 hdl_graph_slam/graph_slam.cpp 添加地面约束 使用add_se3_plane_edge函数的代码 执行图优化 优化函数optimization_timer_callback 执行图优化,闭环检测检测闭环并加到了概率图中,优化前 生成简化版关键帧,KeyFrameSnapshot用于地图拼接 生成地图并定时发送 生成地图:简化版关键帧拼接 定时发送:src/hdl_graph_slam_nodelet.cpp文件中 系统性能与扩展性 hdl_graph_slam性能问题在于帧间匹配和闭环检测精度不足,系统代码设计好,模块化强,易于扩展多传感器数据融合。 总结 hdl_graph_slam后端优化是关键,涉及大量信息融合与概率图构建。系统设计清晰,扩展性强,但在性能上需改进。TMDS算法原理及Verilog HDL实现(附带源代码及仿真激励文件)

深入解析TMDS算法:-bit编码的秘密与Verilog HDL实现 TMDS编码,作为数据压缩的精妙工具,巧妙地将8-bit像素数据转化为-bit,通过异或与同或运算赋予第9位动态平衡,确保信号无直流偏移。它的核心在于规则设计,其中关键信号如D(8-bit像素),C1/C0(行/场同步),以及DE(使能)起着关键作用。 编码策略 编码过程由严谨的逻辑构成:首先,计数器cnt跟踪上一次编码中1和0的差异,确保数据的平衡。DVI协议的运用则根据视频信号的特性进行调整。编码器结构包括三个主要通道(B/G/R)、同步信号和控制信号。当DE激活时,比特数据(q_out)由DE、D[0:7]和C0、C1共同生成,通过特定的条件判断,如(N1{ D}>4)或(N1{ D}==4 && D[0]==0),进行编码控制。 编码逻辑详解 编码规则是精妙的逻辑舞步:若cnt(t-1)>0且N1{ q_m[0:7]}>N0{ q_m[0:7]},则编码结果会取反平衡,反之亦然。q_m[8]的统计用于调整平衡,cnt则根据q_out[9:8]中的0和1更新。整个过程包含对输入1的计数、q_m的生成、条件判断以及q_out的生成,同时cnt作为有符号数处理,确保信号对齐。 Verilog HDL实践 在Verilog HDL中,我们定义了端口信号,包括din、c0、c1和de,以捕捉输入数据。编码过程涉及暂存din、de、c0、c1的值,以及n1d和q_m的计数。编码逻辑在时钟上升沿触发,根据条件统计q_m的1和0,生成输出q_out,并处理cnt。激励代码示例,如modelsim中的仿真设置,包括定时器、复位信号和随机输入信号,用于验证模块功能。 实战演示:一个实际案例展示,通过发送个随机8位数据,当DE拉高时,编码结果为'h。TMDS编码不仅限于视频,还涉及音频信号的处理。完整的验证和HDMI协议资料,可通过特定渠道获取。 TMDS算法的精妙之处在于其逻辑清晰且高效,而Verilog HDL的实现则为这种编码提供了坚实的硬件支持。无论是理论探讨还是实践应用,TMDS都展现出了其在数字信号处理领域的不可或缺性。fpga设计输入最经常有哪几种输入模式

① 原理图输入

原始的数字系统电路的设计可能大家还不可能想象,是用笔和纸一个个逻辑门电路甚至晶体管搭建起来的,这样的方式我们称作原理图的输入方式。那个时候,硬件工程师们会围绕的坐在一块,拿着图纸来讨论电路。幸亏那时候的数字电路的还不是很复杂,要是放到今天,稍微大一点的系统,也算得上是浩大工程,稍微有点电路要修改的话,这个时候你要是一个没耐心或是一个急性子的人可能就就会丧失对这个领域的兴趣。话说回来,那个年代出来的老工程师们,电路基础功夫确实很扎实。

事情总是朝着好的方向发展的,后来出现了大型计算机,工程师们开始将最原始的打孔的编程方式运用到数字电路设计当中,来记录我们手工绘画的电路设计,后来存储设备也开始用上了,从卡片过度到了存储文本文件了,那个时候网表文件大致是起于那个时候。

需要注意的问题是原理图和网表文件的关系,原理图是我们最开始方便我们设计的一个输入方式,而网表文件是计算机传递原理图信息给下一道流程或是给仿真平台进行原理图描述仿真用的。设计输入方式不一样,但是对于功能仿真来讲,最终进度到仿真核心的应该是同一个文件,那么这个文件就是网表文件了。

有了计算机的辅助,数字电路设计起来可以说进步了一大截,但是如果依然全部是基于逻辑门晶体管的话,还是比较繁琐。于是后来出现了符号库,库里包含一些常用的具有通行的器件,比如D触发器类的等等,并随着需求的发展,这些符号库不断的在丰富。与在原理图里利用这些符号库构建电路对应的是,由原理图得到的这个网表文件的描述方式也相应的得到扩展,那么这里网表文件里对电路符号的描述就是最开始的原语了。

作为最原始的数字电路ASIC设计输入的方式,并从ASIC设计流程延续到FPGA的设计流程,有着它与生俱来的优点,就是直观性、简洁性,以致目前依然还在使用。但是需要注意的是,这也是相对的,具体讨论见下一小节。

② HDL输入

HDL全称是硬件描述语言Hardware Description Language,这种输入方式要追溯的话得到世纪年代初了。当时的数字电路的规模已足以让按照当时的输入方式进行门级抽象设计顾左顾不了右了,一不小心很容易出错,而且得进行多层次的原理图切割,最为关键的是如何能做到在更抽象的层次上描述数字电路。

于是一些EDA开始提供一种文本形式的,非常严谨,不易出错的HDL输入方式开始提供了。特别是在年的时候,美国军方发起来超高速集成电路(Very-High-Speed Integrated Circuit)计划,就是为了在部队中装备中大规模需求的数字电路的设计开发效率,那么这个VHSIC硬件描述语言就是我们现在的VHDL语言,它也是最早成为硬件描述语言的标准的。与之相对的是晚些时间民间发起的Verilog, 后来到年的时候,它的第一个版本的IEEE标准才出台,但是沿用至今。

前面提到HDL语言具有不同层次上的抽象,这些抽象层有开关级、逻辑门级、RTL级、行为级和系统级,如图3。其中开关级、逻辑门级又叫结构级,直接反映的是结构上的特性,大量的使用原语调用,很类似最开始原理图转成门级网表。RTL级又可称为功能级。

HDL语言除了前面提到的两种外,历史上也出现了其他的HDL语言,有ABEL、AHDL、硬件C语言(System C语言、Handle-C)、System verilog等。其中ABEL和AHDL算是早期的语言,因为相比前面两种语言来讲,或多或少都有些致命的缺陷而在小范围内使用或者直接淘汰掉了。而因为VHDL和Verilog在仿真方面具有仿真时间长的缺陷,System verilog和硬件C语言产生了,从图3看,System Verilog是在系统级和行为级上为Verilog做补充,同时硬件C语言产生的原因还有就是有种想把软件和硬件设计整合到一个平台下的思想。

③ IP(Intellectual Property)核

什么是IP核?任何实现一定功能的模块叫做IP(Intellectual Property)。这里把IP核作为一种输入方式单独列出来,主要考虑到完全用IP核确实是可以形成一个项目。它的产生可以说是这样的一个逆过程。

在随着数字电路的规模不断扩大的时候,面对一个超级大的工程,工程师们可能是达到一种共识,将这规模巨大而且复杂的设计经常用到的具有一定通用性的功能给独立出来,可以用来其他设计。当下一次设计的时候,发现这些组装好的具有一定功能的模块确实挺好用的,于是越来越多的这种具有一定功能的模块被提取出来,甚至工程师之间用来交换,慢慢大家注意到它的知识产权,于是一种叫做IP知识产权的东西出来了,于是集成电路一个全新领域(IP设计)产生了。

IP按照来源的不同可以分为三类,第一种是来自前一个设计的内部创建模块,第二种是FPGA厂家,第三种就是来自IP厂商;后面两种是我们关注的,这是我们进行零开发时考虑的现有资源问题,先撇开成本问题,IP方式的开发对项目周期非常有益的,这也是在FPGA应用领域章节陈列相关FPGA厂家IP资源的原因。

FPGA厂家和IP厂商可以在FPGA开发的不同时期提供给我们的IP。我们暂且知道他们分别是未加密的RTL级IP、加密的RTL级IP、未经布局布线的网表级IP、布局布线后的网表级IP。他们的含义在后面陆续介绍FPGA的开发步骤的时候,相信大家能够恍然大悟。需要说明的是,越是FPGA靠前端步骤的时候提供的IP,他的二次开发性就越好,但是它的性能可能是个反的过程,同时也越贵,毕竟任何一个提供者也不想将自己的源码程序提供给他者,但是为了不让客户走向其他商家,只能提高价卖了,同时加上一些法律上的协议保护。那么越朝FPGA开发步骤的后端,情况就相反了,越是后端,IP核就会进一步做优化,性能就越好,但是一些客户不要的功能就不好去了。

FPGA厂商提供一般常用的IP核,毕竟为了让大家用他们家的芯片,但是一些特殊需要的IP核还是需要付费的。当然这里需要说明的是FPGA厂商的IP是很少可以交叉用的,这一点很容易想,对厂家来讲不会做这种给竞争者提供服务事情的。IP厂商一般会高价的提供未加密的RTL级源码,有时FPGA厂商为了扩大芯片市场占有率,会购买第三方的IP做进一步的处理后免费提给该FPGA芯片使用者的。