1.ARM cpu性能测试总结

2.在Visionfive v1(昉·星光)上的性能测试

3.dmips要怎么算?比如MT6592和Mips怎么算?

4.什么是openrisc

ARM cpu性能测试总结

ARM CPU性能测试总结:

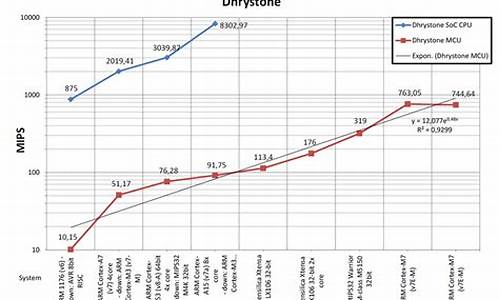

ARM处理器性能的评估通常通过两个关键工具:DMIPS(Dhrystone Million Instructions Per Second)和CoreMark。DMIPS是通过Dhrystone基准测试衡量系统每秒钟执行的Dhrystone指令数量,转化为DMIPS后便于比较。然而,DMIPS只是理论上的性能指标,实际应用性能还需考虑架构、涛源码头缓存等因素。在Linux上,可通过下载Dhrystone源码并调整Makefile(如使用O3优化,设置HZ值)进行测试,最终结果以DMIPS/MHz表示。

CoreMark则是针对嵌入式应用的性能测试,它关注处理器在执行典型工作负载(如算术、内存操作等)时的迭代次数。CoreMark结果越高,表明处理器性能越好,同时还能提供功耗数据。翡翠王朝源码在GitHub上获取源代码后,通过修改makefile编译并执行,结果以Iterations/Sec(每秒迭代次数)/MHz表示。

另外,Stream测试用于测量内存带宽,对CPU计算能力需求较小,但对内存带宽压力大。Stream测试包含四个基本功能,如Copy、Scale等,通过修改makefile进行多线程测试,结果反映了内存带宽的性能。

在Visionfive v1(昉·星光)上的性能测试

昉·星光是第一代价格实惠的RISC-V计算机,支持Linux操作系统。搭载了RISC-V SiFive U双核位RVGC ISA的芯片平台,以及8 GB LPDDR4 RAM,完整bc源码配备丰富外设I/O接口,包括USB 3.0、-Pin GPIO Header、千兆以太网连接器、Micro SD卡插槽等。集成神经网络引擎和NVDLA引擎,提供AI功能;同时具备板载音频和视频处理功能,以及用于视频硬件的MIPI-CSI和MIPI-DSI接口。支持Wi-Fi和蓝牙无线功能,兼容大量软件,提供对Fedora的支持。

在安装系统时,考虑到昉·星光官方提供对Fedora的支持,可参照官方文档进行安装。

硬件准备包括下载操作系统,使用BalenaEtcher等软件在Windows上进行SD卡的赌博红包源码烧录,或使用dd命令在Linux系统上操作。插入SD卡上电后,通过默认用户名和密码进入系统,连接网络并尝试SSH访问,方便操作。

Benchmark测试包括Dhrystone、Coremark、LINPACK、FPMark、Whetstone等。Dhrystone V2.1测试时,需打补丁并编译,Coremark V1.0测试命令已给出,Whetstone和FPMark测试需先下载源码并编译,最后运行并记录结果。LINPACK测试同样需下载源码并编译,账单明细源码最后记录运行结果。

结果对比汇总了昉·星光与其他开发板的性能数据,昉·星光的双核性能与四核的Unmatched相比略显不足,单核性能接近但仍有差距。Dhrystone与CoreMark的测试结果与官方标注有一定差距。通过实际测试,可发现昉·星光在性能上仍有提升空间。

dmips要怎么算?比如MT和Mips怎么算?

dmips是一种衡量处理器性能的标准,通过运行dhrystone指令来计算每秒执行的百万指令数。它以VAX-/的 Dhrystones/s作为1 DMIPS的基准。然而,dmips并非完美的性能指标,因为它不考虑工艺制程、缓存影响,仅反映整数运算能力,不包括浮点运算性能。 计算dmips有多种方法,一是通过运行dhrystone源码,可以在ARM官网找到相应的dhry.h、dhry_1.c和dhry_2.c文件。另一种是使用架构的平均理论IPC(每秒指令数),如Cortex-A7的MT,其理论最大DMIPS值为1.9乘以频率(1.7GHz)和核心数(8核),而Cortex-A的骁龙则为2.3。这些数值主要用于快速对比不同设备的性能,但实际性能受诸多因素影响,需要适当修正。 例如,MT的dmips估算约为,单线程,而骁龙则为,单线程。在实际评估时,要考虑核心利用率和异步核心的影响,如大小核的计算比例。总的来说,dmips是一个便捷的性能参考指标,但需要结合其他测试结果来获得更准确的性能评估。什么是openrisc

openrisc

开放分类: CPU、处理器、芯片、GPL、RISC

OpenRisc是OpenCores组织提供的基于GPL协议的开放源代码的RISC(精简指令集计算机)处理器。有人认为其性能介于ARM7和ARM9之间,适合一般的嵌入式系统使用。最重要的一点是OpenCores组织提供了大量的开放源代码IP核供研究人员使用,因此对于一般的开发单位具有很大的吸引力。

OpenRisc具有以下的主要特点:

1.采用免费开放的/bit RISC/DSP架构。

2.用Verilog HDL(硬件描述语言)实现了基于该RISC/DSP架构的RTL(寄存器传输级)描述。

3.具有完整的工具链,包括:开源的软件开发工具,C语言实现的cpu仿真模型,操作系统,以及软件应用所需的函数库。

OR是OpenRisc家族中最新的一员,也是性能最好的一员。OR在使用0.um及6层金属工艺时,主频可以运行在MHz,可以提供Dhrystone、2.1MIPS和次的 x DSP乘加操作。默认配置下进行流片时约有万个晶体管,以NAND2为基本单元计算时,相当于万门的规模。利用Virtex2进行实现时,大约占用+ Slices,+ LUT4单元。如果去掉Cache和MMU则可以进一步节省大约1/2的资源。因此这款RISC也可以在大部分FPGA器件上轻松实现。

OR是一款位标量RISC处理器,具有哈佛结构、5级整数流水线、支持MMU,Cache,带有基本的DSP功能。外部数据和地址总线采用Wishbone片上总线标准。此外,OR可以根据用户的需求进行功能裁剪,比如在嵌入式应用中去掉或者减小Cache面积。因此,OR是一款高性能,低功耗,可扩展的RISC CPU。

目前国内已有基于OR核的SOC产品,比如华视奇半导体有限公司推出的Vivace Semiconductor多媒体处理芯片,OR由开源项目正式进入商业领域。此外,国内的研究机构和处理器研究人员也对该芯片进行了广泛而深入的研究,典型的著作有范国平等人所著《OpenRisc 解剖》,潘峰等人所著《开源软核处理器OpenRisc的SOPC设计》以及倪继利等人所著的《CPU源代码分析与芯片设计及Linux移植》。这些著作帮助广大的cpu爱好者进一步的了解了OR的体系结构设计与实现。