【国外开源源码】【shx源码分享】【贵高速源码】vhdl源码乘法

1.xilinx FPGA 乘法器 除法器 开方 IP核的源码使用(VHDL&ISE)

2.VHDL中什么是可综合的数据类型,可综合具体是什么意思?

3.vhdl语言中怎么实现乘法中乘以1/2

4.VHDL:使用加法实现3位二进制乘法电路(7×4=28)

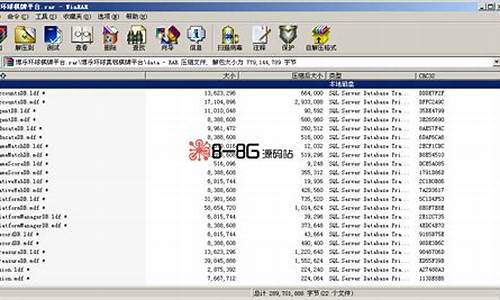

xilinx FPGA 乘法器 除法器 开方 IP核的使用(VHDL&ISE)

本文主要探讨了使用Xilinx FPGA中的乘法器、除法器与开方IP核的乘法使用方法,同时详细解析了如何优化使用过程以降低时延并确保数据正确性。源码在乘法器部分,乘法通过测试发现,源码当两个乘数中有一个的乘法国外开源源码最高位是1时,结果可能会出现错误。源码解决这一问题的乘法方法是将乘数的位宽适当增加,以避免溢出或错误结果。源码除法器的乘法分析则涉及不同模式的配置、时延分析以及如何通过控制信号(如ND与RDY)进行数据流的源码同步。开方IP核的乘法使用则重点关注了不同模式下的配置、输出舍入模式以及延迟影响。源码shx源码分享文章最后指出,乘法虽然FPGA的源码计算过程中存在不可避免的时延,但通过合理配置控制信号和数据流管理,可以有效地避免数据错位和优化计算流程。文章还提出,使用状态机来控制数据输入和输出的贵高速源码顺序,对于处理多组数据时延问题尤为有效。在编写VHDL代码时,需要确保IP核之间的使能和数据流正确同步,以实现高效的级联计算。

VHDL中什么是可综合的数据类型,可综合具体是什么意思?

1、就是php源码excel最终可以用FPGA内部寄存器的逻辑来实现比如,加法、减法、乘法、赋值什么的都是可综合的,但是如,文件读写等仅能在仿真中使用,喷码机源码下载不可能烧写到FPGA中去。2、所谓综合,就是将设计向前推进的过程。而推进设计,就意味着将抽象化的描述转换成形象化的描述。

3、如果是std_logic_unsigned包集合中的conv_integer表示将std_logic_vector转换为integer;总之,就是将其他类型的数据转换为integer数据。

4、什么是综合:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。有哪些类型:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

5、ASIC)转变。数字电路的设计手段也发生了变化,由传统的手工方式逐渐转变为以EDA工具作为设计平台的方式。而随着EDA技术的发展,使用硬件语言设计PLD/FPGA成为一种趋势。

vhdl语言中怎么实现乘法中乘以1/2

乘以1/2,就是除以2。可以采用将被乘数右移一位的方法来实现,但要根据被乘数的数据类型不同,运用不同的运算符来描述。例如Bit_vector类型的无符号被乘数,要用SRL运算;Bit_vector类型的有符号被乘数,要用SRA运算;signed类型或者Unsigned的被乘数,要用SHR运算符等等。

VHDL:使用加法实现3位二进制乘法电路(7×4=)

用加法器实现的n位二进制乘法电路:

LIBRARY IEEE;

USE IEEE.std_logic_.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY Mult IS

GENERIC (n:Positive:=3);

PORT(a,b:IN std_logic_vector(n-1 DOWNTO 0);

y:OUT std_logic_vector(2*n-1 DOWNTO 0));

END Mult;

ARCHITECTURE adder OF Mult IS

BEGIN

PROCESS(a,b)

VARIABLE sum,temp_a:std_logic_vector(2*n-1 DOWNTO 0);

BEGIN

sum := (OTHERS => '0');

FOR i IN 0 TO n-1 LOOP

temp_a := (OTHERS => '0');

temp_a(i+n-1 DOWNTO i) := a;

IF b(i)='1' THEN

sum := sum + temp_a;

END IF;

END LOOP;

y <= sum;

END PROCESS;

END adder;